处理器

处理器架构

- 普林斯顿架构:存储器同时存储指令和其他数据

- 哈佛架构:数据存储和指令存储分开

处理器性能

执行时间 = 指令数 x CPI x 时钟周期

或: $$ CPI = CPI_1\times p_1+…+CPI_n\times p_n $$ 性能提升方法:

- 优化编译技术(减少指令数)

- 快速电路技术或更为先进的电路结构(减少时钟周期)

寄存器 VS 存储器

- 寄存器:以编号进行访问,可同时访问不同寄存器。

- 存储器:以地址进行访问,不可同时访问不同地址,相邻数据的地址相差4字节。

数据单位约定

在32位MIPS中,1 word = 4 bytes = 32 bits,相邻数据的地址相差4字节。

|

|

MIPS汇编指令

汇编优化相关问题

-

算数&逻辑指令11bit冗余能否利用起来?

额外11bit用于移位量&功能码。好处:寄存器算术操作只占用一种操作码,指令集可以使用其他操作码支持更多种指令。

-

分支可能的地址范围有32位,如何用16bit表示?

采用基址+偏移地址的寻址方式。

addr « 2:将直接地址转换为字节地址。

-

带立即数的分支指令立即数如何编码?

MIPS没有带立即数的分支指令,使用比较指令(slti、sltiu等)+ 分支指令组合实现。

-

访存可能的地址有32位,如何用21bit表示?

采用基址+偏移地址的寻址方式进行访存(5 bit:寄存器 16 bit:立即数)。

-

跳转可能的地址有32位,如何用26bit表示?

j小范围,jr大范围。

寻址方式

- 寄存器寻址:找到对应的寄存器,从寄存器中取数/写数。如:R type(add)。

- 立即数寻址:指令中的立即数可以被直接使用。如:I type(addi)

- 基址寻址:目标地址=基址(存储于寄存器中)+ 立即数。如:lw,sw

- PC相对寻址:PC+立即数。如:beq

- 伪直接寻址:固定PC的高4位不变。如:j

MIPS过程调用

-

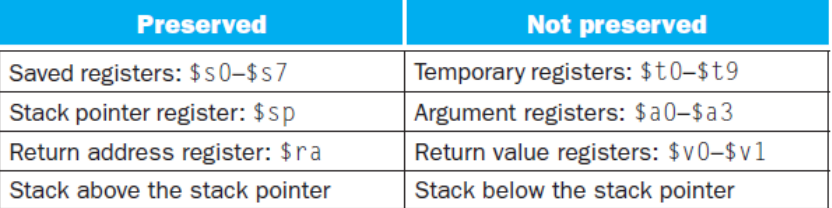

Preserved(子程序不改变这些寄存器的数据,如果子程序要用,需要子程序维护好)

-

Not Preserved(子程序可以改变这些寄存器的数据,如果主程序要用,需要主程序维护好)

考虑以下汇编:

|

|

对应:

|

|